# MOSFET ZTC Condition Analysis for a Self-biased Current Reference Design

Pedro Toledo<sup>1,2</sup>, Hamilton Klimach<sup>2</sup>, David Cordova<sup>1,2</sup>, Sergio Bampi<sup>2</sup> and Eric Fabris<sup>1,2</sup>

<sup>1</sup>NSCAD Microeletrônica, UFRGS, Porto Alegre, RS, Brazil <sup>2</sup>PGMicro, UFRGS, Porto Alegre, RS, Brazil e-mail: toledo@nscad.org.br, hamilton.klimach@ufrgs.br, david@nscad.org.br, bampi@inf.ufrgs.br, fabris@inf.ufrgs.br

## ABSTRACT

In this paper a self-biased current reference based on Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) Zero Temperature Coefficient (ZTC) condition is proposed. It can be implemented in any Complementary Metal-Oxide-Semiconductor (CMOS) fabrication process and provides another alternative to design current references. In order to support the circuit design, ZTC condition is analyzed using a MOSFET model that is continuous from weak to strong inversion, showing that this condition always occurs from moderate to strong inversion in any CMOS process. The proposed topology was designed in a 180 nm process, operates with a supply voltage from 1.4V to 1.8 V and occupies around 0.010mm<sup>2</sup> of silicon area. From circuit simulations our reference showed a temperature coefficient (TC) of 15 ppm/°C from -40 to +85°C, and a fabrication process sensitivity of  $\sigma/\mu = 4.5\%$  for the current reference, including average process and local mismatch variability analysis. The simulated power supply sensitivity is estimated around 1%/V.

Index Terms: MOSFET ZTC Condition, Current Reference Source and Low Temperature Coefficient.

## **I. INTRODUCTION**

Current references are essential building blocks for analog, mixed-signal and RF designs, often being used for biasing of analog subsystems inside the chip. The usual way to generate a current reference is through the implementation of a voltage reference [1], [7], [10], [16] and applying this voltage over a resistive device [2]. Another approach is using a device where a physical property or condition naturally establishes an operating current, which can be used as a reference [3]–[6], [8], [9], [14], [18].

Any kind of Direct Current (DC) reference, either a voltage or a current one, must offer appreciable thermal stability and power supply rejection, as its main characteristics. In addition, adequate fabrication repeatability ensures that the biasing operation point of the analog blocks is almost the same in every fabricated chip, and reveals how sensitive the current generator is with respect to fabrication process variations [19].

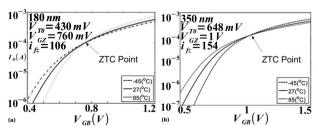

The main idea of this paper is to use the physical condition of MOSFETs called "zero temperature coefficient" (ZTC) to implement a circuit topology where the resulting current offers low sensitivity to temperature and process variations. This condition defines a biasing point where the drain current presents small temperature sensitivity, as can be seen in Fig. 1. The ZTC current condition occurs for every MOSFET in any technology, for N-Channel Metal-Oxide-Semiconductor (NMOS) and P-Channel Metal-Oxide-Semiconductor (PMOS) transistors, and it is the effect of mutual cancellation of the channel carrier mobility and the threshold voltage dependencies on temperature [4]. Remembering that the drain current increases when mobility increases and when threshold voltage decreases, and that mobility and threshold voltage both decrease when temperature increases, it can

Figure 1. NMOS ZTC point for (a) 180 and (b) 350nm bulk-CMOS processes.

be proved that both effects can cancel each other at a certain bias point. Fig. 1 presents the drain current vs gate-source voltage of NMOS transistors under three temperatures for two different fabrication process, and in both figures a convergence point can be seen for the three I-V curves drawn.

The traditional analysis of this effect presented in literature is based on the strong inversion quadratic MOSFET model [4]. In this work we use a different analytical approach, based on a continuous MOSFET model that can predict its behavior from weak to strong inversion [11][21]. Based on this analysis, we verify that the ZTC point occurs from moderate to strong inversion for any CMOS process.

This paper is organized as follows. In Section II, an analytical formulation and the discussion about the ZTC operating point using an all-region CMOS compact model are presented. In Section III, simulation results from three fabrication processes are presented, regarding the ZTC operating point. After selecting a fabrication process for our design, in Section IV a self-biased CMOS current reference topology is proposed and described. The simulation results are presented in section V, followed by comparisons to other references proposed in literature. Finally, in section VI, the concluding remarks are drawn.

## **II. MOSFET ZTC CONDITION**

MOSFET ZTC condition derives from mutual cancellation of mobility and threshold voltage dependencies on temperature [4]-[5], at a particular gate-to-bulk voltage bias. The drain current ZTC operating bias point was firstly defined in [4] and after in other correlated publications, always based on strong inversion quadratic MOSFET model. From [4], ZTC operating point is given by Eqs. (1) and (2).

$$V_{GZ} = V_{T0}(T_0) + nV_{SB} - \alpha_{V_{T0}}T_0$$

(1)

$$I_{DZ} = \frac{\mu(T_0)T_0^2 C'_{ox}}{2n} \left(\frac{W}{L}\right) \alpha_{V_{T0}}^2$$

(2)

where  $T_0$  is the room temperature,  $V_{T0}(T0)$  is the threshold voltage at room temperature, *n* is the slope factor,  $V_{SB}$  is the source-bulk voltage,  $\alpha_{VT0}$  is the thermal coefficient of the threshold voltage (a negative parameter, since  $V_{T0}$  decreases with temperature),  $\mu(T_0)$  is the low field mobility at room temperature,  $C'_{ax}$  is the oxide capacitance per unit of area and (W/L)is the transistor aspect ratio. and are defined as gatebulk and drain current ZTC bias point, respectively.

Fig. 1 (a) shows the drain current (in a log scale) as a function of gate-bulk voltage  $(V_{GB})$  of a saturated long-channel NMOSFET, simulated under tempera-

tures ranging from -45 to +85°C, for a 180 nm process. ZTC operation point can be seen around  $V_{GB} \approx$  760mV for a transistor with  $V_{T0} = 430$ mV, resulting that ZTC point occurs for an overdrive voltage around 330mV, meaning the transistor operates in strong inversion. Fig. 1 (b) shows the same for an NMOS transistor in a 350 nm CMOS process.

In a more general analysis, we can suppose that the ZTC condition can also happen in moderate inversion and a more complete MOSFET model must be used, such as one presented in [11], which describes continuously transistor behavior at any inversion level. The well-known Advanced Compact Model (ACM) is a design-oriented MOSFET model suitable for analog integrated-circuit design. From this model, Eqs (3) and (4) give the drain current of a long channel NMOSFET.

$$I_{D} = I_{F} - I_{R} = I_{S}(i_{f} - i_{r})$$

(3)

$$I_{S} = \mu C_{ox}' n \, \frac{\phi_{t}^{2} \, W}{2 \, L} \tag{4}$$

where  $I_{F(R)}$  is the forward (reverse) current,  $i_{f(r)}$  is the forward (reverse) inversion coefficient,  $I_s$  is the normalization current, and  $\phi_t$  is the thermal voltage.

Also from this model, Eqs. (5), (6) and (7) relate source and drain inversion coefficients (forward and reverse),  $i_f$  and  $i_r$ , with the three external voltages applied to transistor terminals,  $V_{GB}$ ,  $V_{SB}$  and  $V_{DB}$ , using bulk terminal as reference.

$$V_{P} - V_{S(D)B} = \phi_{t} \left[ \sqrt{1 + i_{f(r)}} - 2 + ln \left( \sqrt{1 + i_{f(r)}} - 1 \right) \right]$$

(5)

$$V_P = \frac{V_{GB} - V_{T0}}{n}$$

(6)

$$V_{T0} = V_{FB} + 2\phi_F + \gamma \sqrt{2\phi_F} \tag{7}$$

where  $V_p$  is called the pinch-off voltage,  $\Upsilon$  is the body effect coefficient,  $V_{FB}$  is the flat band voltage and  $\phi_F$  is the Fermi potential at the bulk of semiconductor under transistor channel.

First order temperature dependence of  $V_{T0}$  can be given by Eqs. (8) and (9) [11].

$$V_{T0}(T) = V_{T0}(T_0) - |\alpha_{T0}|(T - T_0)$$

(8)

$$\left|\frac{\delta V_{T0}}{\delta T}\right|_{T=T_0} = |\alpha_{T0}| = \frac{1}{T_0} \left(1 + \frac{\gamma}{\sqrt{2\phi_F}}\right) \left(\frac{E_G}{2q} - \phi_F\right)$$

(9)

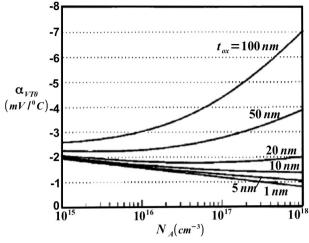

where q is the electron charge and  $E_{G}$  is the silicon band-gap energy. Fig. 2 presents expected values

Figure 2.  $\alpha_{VT0}$  vs  $N_A$  for different  $t_{ox}$  [13].

for  $\alpha_{VT0}$  for wide ranges of doping concentration  $(N_A)$  and oxide thickness  $(t_{ax})$  [13]. The target-technologies for this study are below 350 nm, which corresponds to  $\alpha_{VT0}$  values between -3.5 and -0.5 mV/°C [13], that is the range used in the following analysis. In addition, Eq. (10) gives the thermal mobility dependence [13].

$$\mu(T) = \mu(T_0) \left(\frac{T}{T_0}\right)^{\alpha_{\mu}} \tag{10}$$

where  $\alpha_{\mu}$  is the temperature dependence power for mobility model. Since the carriers in inversion layer of transistors undergo several scattering mechanisms,  $\alpha_{\mu}$  is negative, and its value depends on prevalent scattering mechanisms (such as Coulombic, phonon, or interface scatterings - all of them interfering on carrier transport). Related to electron mobility and under room temperature this parameter varies in a range from -1.5 for high doping concentrations to – 2.4 for light doping concentrations [13].

If one derives the drain current expression for temperature in saturation region  $(i_r << i_f)$ , the condition where its temperature dependence is negligible can be found, i.e.,  $\frac{\delta I_D}{\delta T}\Big|_{T=T_0} \approx 0$ . Using Eq. (3) and deriving it as a function of temperature.

$$\frac{\delta}{\delta T} \left( I_{S} i_{f} \right) \Big|_{T=T_{0}} = \left. I_{S} \frac{\delta i_{f}}{\delta T} \right|_{T=T_{0}} + \left. i_{f} \frac{\delta I_{S}}{\delta T} \right|_{T=T_{0}}$$

(11)

The  $\frac{\partial I_f}{\partial T}\Big|_{T=T_0}$  can be found deriving Eqs. (5) and (6) with respect to temperature, to find that

$$\frac{\delta}{\delta T} \left( \frac{V_{GB} - V_{T0}}{n} - V_{SB} \right) = \frac{\delta}{\delta T} \left( \phi_t \left[ \sqrt{1 + i_f} - 2 + \ln\left(\sqrt{1 + i_f} - 1\right) \right] \right)$$

(12)

As  $V_{GB}$  and  $V_{SB}$  are temperature independent,

$$\frac{\delta}{\delta T} \left( \frac{-V_{T0}}{n} \right) = \frac{\delta \phi_t}{\delta T} \left[ \sqrt{1 + i_f} - 2 + \ln\left(\sqrt{1 + i_f} - 1\right) \right] + \phi_t \frac{\delta}{\delta T} \left( \sqrt{1 + i_f} - 2 + \ln\left(\sqrt{1 + i_f} - 1\right) \right)$$

(13)

Assuming that  $\frac{\delta \phi_t}{\delta T} = \frac{\phi_t}{T}$  and putting (8) in (13)

$$\begin{split} & \frac{\delta}{\delta T} \left( \frac{|\alpha_{VT0}|}{n} \right) = \frac{\phi_t}{T} \left[ \sqrt{1 + i_f} - 2 + \ln\left(\sqrt{1 + i_f} - 1\right) \right] \\ & + \phi_t \frac{\delta}{\delta T} \left( \sqrt{1 + i_f} - 2 + \ln\left(\sqrt{1 + i_f} - 1\right) \right) \end{split}$$

(14)

Noting that the second term of the right branch of the Eq. (14) is equal to

$$\begin{split} \frac{\delta}{\delta T} \Big( \sqrt{1 + i_f} - 2 + \ln \left( \sqrt{1 + i_f} - 1 \right) \Big) &= \\ \Big( \frac{1}{2 \left( \sqrt{1 + i_f} + 1 \right)} \Big) \frac{\delta i_f}{\delta T} \end{split} \tag{15}$$

And putting Eq. (15) in (14),

$$\frac{\delta}{\delta T} \left( \frac{|\alpha_{VT0}|}{n} \right) = \frac{\phi_t}{T} \left[ \sqrt{1 + i_f} - 2 + \ln\left(\sqrt{1 + i_f} - 1\right) \right] \\ + \phi_t \left( \frac{1}{2\left(\sqrt{1 + i_f} + 1\right)} \right) \frac{\delta i_f}{\delta T}$$

(16)

Isolating the term  $\frac{\delta i_f}{\delta T}$  from Eq. (16), we get

$$\frac{\delta i_f}{\delta T} = 2\left(\sqrt{1+i_f}+1\right) \\ \left(\frac{|\alpha_{VT0}|}{n\phi_t} - \frac{1}{T}\left(\sqrt{1+i_f}-2 + \ln\left(\sqrt{1+i_f}-1\right)\right)\right)$$

(17)

The derivative of normalization current regarding the absolute temperature can be found from Eq. (4) and Eq. (10).

$$\frac{\delta I_S}{\delta T} = \frac{1}{2} C'_{ox} n \, \frac{W}{L} \frac{\delta}{\delta T} (\phi_t^2 \mu) \tag{18}$$

where  $\delta n / \delta T = 0$ . After some algebra,

$$\frac{\delta I_S}{\delta T} = \frac{1}{2} C'_{ox} n \, \frac{W}{L} \left( \frac{\delta \mu}{\delta T} \phi_t^2 + \frac{\delta \phi_t^2}{\delta T} \mu \right) \tag{19}$$

Therefore, we can use  $\frac{\delta\mu}{\delta T} = \frac{\alpha_{\mu}\mu}{T}$  and  $\frac{\delta\phi_t^2}{\delta T} = \frac{2\phi_t}{T}$  in (19), we obtain

$$\frac{\delta I_S}{\delta T} = I_S \left(\frac{\alpha_\mu + 2}{T}\right) \tag{20}$$

Journal of Integrated Circuits and Systems 2015; v.10 / n.2:103-112

Finally, applying Eqs. (20) and (17) in (11), and after isolating some terms one can find:

$$\frac{|\alpha_{VT0}|T}{n\phi_t} = \frac{|\alpha_{VT0}|q}{nk} = \left(\frac{\alpha_{\mu}+2}{2}\right) \left(\frac{-i_{fz}}{\sqrt{1+i_{fz}}+1}\right) + \left[\sqrt{1+i_{fz}} - 2 + \ln\left(\sqrt{1+i_{fz}} - 1\right)\right]$$

(21)

where k is the Boltzmann constant and  $i_{fz}$  is defined as ZTC forward inversion level. Eq. (21) shows that if the transistor is biased such that the inversion level at source is  $i_{fz}$ , the drain current is insensitive to temperature.

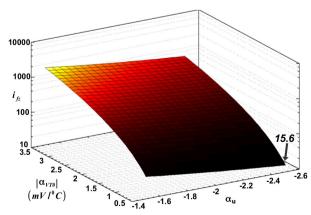

Fig. 3 shows the ZTC forward inversion level surface (ZTCS), i.e., all possible solutions of Eq. (21) for ZTC bias condition as a function of values for  $\alpha_{\mu}$  and  $\alpha_{VT0}$ . The ZTCS shows that the minimum ZTC forward inversion level is around 15.6 for  $\alpha_{\mu} = -2.5$  and  $\alpha_{VT0} = -0.5 \text{ mV/°C}$ . Since inversion coefficient  $i_f = 3$  means the condition where  $V_{GB} = V_{T0}$  from Eqs. (5) and (6), one can conclude that ZTC bias condition always occurs for gate-bulk voltages larger than threshold voltage. Also, it is visible that ZTC inversion coefficient  $(i_{fc})$  is only slightly dependent on  $\alpha_{\mu}$ , when compared to  $\alpha_{VT0}$  dependence, justifying the usual choice  $\alpha_{\mu} \approx -2$  as a reasonable consideration for design purposes [4].

In order to see how far ZTC bias point is from threshold voltage (the overdrive voltage for ZTC bias point), for  $V_s = 0$ , the  $i_{fz}$  can be directly applied in Eq. (5) and (6),

$$V_{GZ} - V_{T0} = V_{OVZ} = n\phi_t f(i_{fz})$$

(22)

where

$$f(i_f) = \sqrt{1 + i_f} - 2 + \ln\left(\sqrt{1 + i_f} - 1\right)$$

(23)

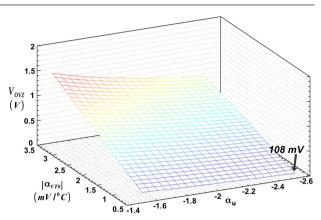

$V_{OVZ}$  is defined as ZTC overdrive voltage. Fig. 4 shows all possible  $V_{OVZ}$  for any  $\alpha_{\mu}$  and  $\alpha_{VT0}$  combination

Figure 3. ZTC forward inversion level Surface (ZTCS).

Figure 4. VOVZ - ZTC overdrive voltage.

in the same range that was used in Fig. 3. The minimum  $V_{OVZ}$  found is around 100 mV meaning that the ZTC bias point is always in moderate inversion condition or above.

Now using the assumption  $\alpha_{\mu} \approx 2$  together with Eq. (21) and (5), a simple expression for ZTC gatebulk voltage ( $V_{GZ}$ - related to  $i_{\hat{\pi}}$ ) is found.

$$V_{GZ} = V_{T0}(T_0) + nV_{SB} - \alpha_{V_{T0}}T_0$$

(24)

Eq. (24) presents the same result already derived from the strong inversion quadratic model in Eq. (1). ZTC drain current, related to  $i_{fz}$ , can be found using Eq. (3)

$$I_{DZ} = I_{FZ} = I_S(T_0)i_{fZ}$$

(25)

#### III. MOSFET ZTC IN COMMERCIAL PROCESSES

ZTC condition of three commercial processes were evaluated through Spice simulations for these devices. Besides 180 and 350 nm already presented in Fig. 1, also the many-threshold transistors of a 130 nm process were verified. Table I shows some results for these transistors, including the threshold voltage  $(V_{T0})$ , the ZTC bias point  $(V_{GZ}, I_{DZ})$  and corresponding inversion level  $(i_{fz})$ . For modern very short-channel nodes, some recent studies show that the ZTC condition still occurs [17].

| Table I. ZTC Operating | Point with | W/L = | 10µm/1 | μm. |

|------------------------|------------|-------|--------|-----|

|------------------------|------------|-------|--------|-----|

| MOSFET           | $V_{_{TO}}(V)$ | $V_{GZ}(V)$ | I <sub>DZ</sub> (μΑ) | i <sub>fz</sub> |

|------------------|----------------|-------------|----------------------|-----------------|

| 180 nm Regular   | 0.43           | 0.76        | 96.27                | 106             |

| 350 nm Regular   | 0.648          | 1.05        | 116.69               | 154             |

| 130 nm Regular   | 0.16           | 0.49        | 222.6                | 106             |

| 130 nm Low-Vt    | 0.1            | 0.44        | 274.8                | 112             |

| 130 nm Low-Power | 0.6            | 0.87        | 128.1                | 74              |

| 130 nm Zero-Vt   | 0.063          | 0.23        | 97.7                 | 32.5            |

## **IV. PROPOSED CURRENT REFERENCE**

Main idea of this paper is to use ZTC vicinity of a NMOS transistor to compensate the thermal drift of a polysilicon resistor, resulting on an equilibrium bias point with small temperature dependence. This circuit topology naturally can be useful as a reference.

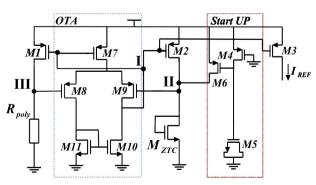

Fig. 5 shows proposed self-biased current reference. It is composed by ZTC NMOS transistor  $(M_{ZTC})$ and a poly resistor  $(R_{boly})$  inside a feed-back loop implemented with an Operational Transconductance Amplifier (OTA). PMOS mirror formed by  $M_1 - M_2$ is for biasing and a start-up circuit is composed by  $M_{4}$  $-M_{c}$  [20].

## A. ZTC vicinity condition

Vicinity of ZTC condition can be analyzed using Eqs. (5) and (6),

$$V_{GB} = n\phi_t f(i_f) + V_{T0}(T) + nV_{SB}$$

(26)

Eq. (26) can be expanded in Taylor series around ZTC forward inversion level  $(i_{\alpha})$ . Therefore, the first order approximation is given by

$$V_{GB}(i_f) \approx V_{GZ} + \left. \frac{\delta V_{GB}}{\delta i_f} \right|_{i_f = i_{fZ}} (i_f - i_{fZ})$$

(27)

where

$$\frac{\delta V_{GB}}{\delta i_f} = n\phi_t \, \frac{\delta f(i_f)}{\delta i_f} \tag{28}$$

After some analytical work, the following relation is obtained:

$$\frac{\delta f(i_f)}{\delta i_f} = \frac{1}{2(\sqrt{1+i_f}-1)}$$

(29)

Combining Eqs. (27), (28) and (29),

Figure 5. Self-biased CMOS Current Reference.

For  $\alpha_{\mu} \approx -2$ , the term  $n\phi_t$  can be extracted from Eq. (21) and can be applied in Eq. (30). Then,

$$V_{GB}(T) \approx V_{GZ} - \frac{\alpha_{VT0} \Delta i_f}{2f(i_{fZ})(\sqrt{1 + i_{fZ}} - 1)}T$$

(31)

where

$$\Delta i_f = \left(i_f - i_{fz}\right) \tag{32}$$

Eq. (31) shows that  $V_{\rm GB}$  presents a linear temperature dependence in vicinity of  $V_{\rm GZ}$ , and that this dependence can be positive or negative, depending on chosen  $\Delta i_{c}$ .

Proposed circuit will be designed in next section for a 180 nm process, using a NMOS transistor where the ZTC bias point occurs in the strong inversion region (Section III). In this way, for design purposes both approximations  $f(i_f) \approx \sqrt{i_{fz}}$  and  $(\sqrt{i_{fz} + 1} - 1) \approx \sqrt{i_{fz}}$ can be adopted and applied in Eq. (31).

$$V_{GB}(T) \approx V_{GZ} - \frac{\alpha_{VT0} \Delta i_f}{2i_{fz}} T$$

(33)

As  $i_f = I_D / I_s$  from Eq. (3), the dependency of  $V_{_{GB}}(T)$  on temperature can be found such that:

$$V_{GB}(T) \approx V_{GZ} - \frac{\alpha_{VT0} \Delta I_D}{2i I_{DZ}} T$$

(34)

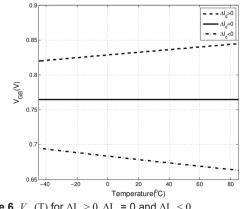

Fig. 6 illustrates the temperature dependence of Eq. (34), showing that if one chooses  $\Delta I_D > 0$  (bias current "after" ZTC point), its derivative is positive,  $\Delta I_D = 0$  is chosen (ZTC point), variation is zero, and if  $\Delta I_D < 0$  (bias current "before" ZTC point), its derivative is negative. One can conclude that a MOSFET operating in vicinity of ZTC point presents a transconductance that can offer a positive or negative thermal dependence, the signal and magnitude of which can be adjusted by chosen bias current.

**Figure 6.**  $V_{GR}(T)$  for  $\Delta I_{D} > 0$ ,  $\Delta I_{D} = 0$  and  $\Delta I_{D} < 0$ .

# B. Circuit Analysis

(

PMOS mirror formed by M1 - M3 is supposed to have an unitary gain in all branches for this analysis. Applying Kirchhoff's voltage law (KVL) over poly resistor, differential input of OTA and ZTC NMOS transistor, Eq. (35) is derived.

$$R(T) \approx R(T_0)(1 + \alpha_1(T - T_0))$$

(35)

where  $V_{OS}$  is the amplifier offset voltage and  $I_{REF}$  is the desired output current. Poly resistor thermal dependence can be approximated as

$$R(T) \approx R(T_0)(1 + \alpha_1(T - T_0))$$

(36)

Using (34), (36) and (35), one can derive

$$(1 - \alpha_1 T_0) R(T_0) I_{REF} + (R(T_0) \alpha_1 I_{REF}) T$$

=  $V_{OS} + V_{GZ} - \frac{\alpha_{VT0} (I_{REF} - I_{DZ})}{2I_{DZ}} T$  (37)

Manipulating temperature dependent and independent parts, Eq. (38) and (39) are derived.

$$(1 - \alpha_1 T_0) R(T_0) I_{REF} = V_{OS} + V_{GZ}$$

(38)

$$R(T_0)\alpha_1 I_{REF} = \frac{\alpha_{VT0}(I_{REF} - I_{DZ})}{2I_{DZ}}$$

(39)

Now the terms  $R(T_{o})$  from (38) and  $I_{DZ}$  from (39) can be isolated

$$R(T_0) = \frac{V_{OS} + V_{GZ}}{I_{REF}(1 - \alpha_1 T_0)}$$

(40)

$$I_{DZ} = \frac{I_{REF}}{1 - \frac{2}{\alpha_{VT0}} R(T_0) \alpha_1 I_{REF}}$$

(41)

Expressions (40) and (41) show the dependence of parameters of devices,  $R(T_0)$  and  $I_{DZ}$ , and the current  $I_{REF}$ , i.e., for a different  $I_{REF}$ , a new sizing for  $R_{ooly}$  and  $M_{ZTC}$  is required.

Another consideration that must be taken into account is the sizing of PMOS mirror  $M_1 - M_2$ . One should consider the  $V_{GB}$  range, defined by Eq. (42).

$$\left| V_{GZ} + \frac{\alpha_{VT0} \Delta I_D T}{2 I_{DZ}} + V_{T0_{P9}} \right| < |V_{GB_{1,2}}|$$

$$< |V_{DD} - V_{DSAT_{10}}|$$

(42)

where  $V_{DSAT_{10}}$  is the overdrive voltage of  $M_{10}$ and  $V_{T0p_9}$  is the threshold voltage of  $M_{0}$ .

Regarding the stability of circuit, Eq. (43) describes the gain loop transfer function.

$$OL(s) = \frac{gm_{8,9}gm_{1,2}r_0(R(T_0) - r_{ztc})}{\left(\frac{s}{p_1} + 1\right)\left(\frac{s}{p_2} + 1\right)\left(\frac{s}{p_3} + 1\right)}$$

$$p_1 = (r_0C_l)^{-1},$$

$$p_2 = (r_{ztc}C_{II})^{-1},$$

$$p_3 = (R(T_0)C_{III})^{-1},$$

(43)

where  $gm_{8,9}$  is the OTA transconductance,  $r_0$  is the equivalent output resistance of OTA,  $r_{ztc}$  is equivalent resistance of ZTC transistor,  $gm_{1,2}$  is the transconductance of PMOS mirror and  $C_I$ ,  $C_{II}$  and  $C_{III}$  are the capacitance related to node I, II and III (Fig. 5).

# C. Circuit Design

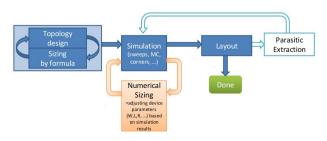

Circuit design was optimized through the Wicked<sup>TM</sup>-MunEDA software [15] along with Cadence<sup>TM</sup> Tools. This tool is useful to improve yield, helping designers to spend less time in optimizing their design for yield, which is certainly an important market demand [12]. Design process was done using the methodology presented in Fig 7 [15]. This approach is composed by an initial analytical sizing, using design formulas described in this work, followed by electrical simulation, numerical sizing, layout and parasitic extraction. Unlike traditional analog design method, where simulation is used only as a verification tool, Wicked-MunEDA software modifies the device geometries iteratively based on simulation results, improving desired parameters. Main advantage of this process is to avoid intensive re-simulation time, which is a common burden in traditional analog design flow [15].

Analytical sizing was done using equations from subsection IV-B, along with the assumption that long channel MOS transistors were used and  $\alpha_{\mu} \approx 2$ . Process documentation and simulation were used to evaluate device parameters.

First step is the definition of  $I_{REF}$  and correspondent resistor  $R(T_0)$  from Eq. (40). Considering  $V_{SB} = 0$  and  $V_{OS} = 0$ ,

$$R(T_0) \approx \frac{V_{T0}(T_0) - \alpha_{VT0}T_0}{I_{REF}(1 - \alpha_1 T_0)}$$

(44)

Figure 7. Numerical Sizing with Wicked™

Then, using (2) in (41), ZTC NMOS ( $M_{ZTC}$  in Fig.5) transistor can be sized.

$$\left(\frac{W}{L}\right)_{ZTC} = \frac{2n\left(\frac{-2}{\alpha_{VT0}}R(T_0)\alpha_1 + \frac{1}{I_{REF}}\right)^{-1}}{\mu(T_0)T_0^2 C'_{ox}\alpha_{VT0}^2}$$

(45)

PMOS mirror  $M_1$ - $M_2$  can also be sized by Eq. (46), taking care about the condition from Eq. (42).

$$\left(\frac{W}{L}\right)_{1,2} = \frac{2nI_{REF}}{\mu(T_0)C'_{ox}(V_{GB} + nV_{SB} - V_{T0P})^2}$$

(46)

Stability can be analytically checked using Eq. (43) or can be simulated.

After initial sizing, numerical size adjustment is done to improve the circuit yield, using "Feasibility Optimization" (FEA) followed by "Deterministic Nominal Optimization" (DNO). FEA enables the circuit designer to check all electrical/geometrical constraints and DNO improves circuit sizing by changing design parameters with unique gradient-based optimization algorithms, as "least-square algorithm" and "parameter distance algorithm". Finally, yield Optimization (YOP) analysis is done [15] in our design method.

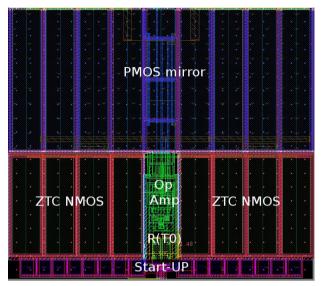

# D. Layout

The reference current layout is small, occupying only 0.01 mm<sup>2</sup>, as shown in Fig. 8. The placement of devices was performed taking all precautions to minimize mismatch effects of global variations. In addition, PMOS mirror and ZTC NMOS were designed to occupy approximately 80% of total layout area, since the sizes of both are dominant factors in determining local mismatch effects.

Final transistor and resistor sizing, after all FEA and DNOS optimization steps, for all devices shown in the schematics of Fig. 5 are given in Table II.

Table II. Device sizing of proposed current reference (180 nm).

| -                           |            | . ,         |  |  |

|-----------------------------|------------|-------------|--|--|

| Device                      | Width (µm) | Length (µm) |  |  |

| R <sub>poly</sub> (7108.2Ω) | 2.62       | 17.65       |  |  |

| M <sub>ztc</sub> (N=8)      | 35         | 10          |  |  |

| M <sub>1</sub> (N=4)        | 50.6       | 10          |  |  |

| $M_{2}(N=4)$                | 50.6       | 10          |  |  |

| M <sub>3</sub> (N=4)        | 50.6       | 10          |  |  |

| M <sub>4</sub>              | 2.75       | 0.18        |  |  |

| M <sub>5</sub> (N=16)       | 5          | 5           |  |  |

| M <sub>6</sub>              | 2.75       | 0.18        |  |  |

| M <sub>z</sub>              | 2.75       | 2           |  |  |

| $M_{s}(N=2)$                | 1.5        | 2           |  |  |

| M <sub>o</sub> (N=2)        | 1.5        | 2           |  |  |

| M <sub>10</sub>             | 1          | 2           |  |  |

| M <sub>11</sub>             | 1          | 2           |  |  |

| *NL is the multiplier pur   | mhor       |             |  |  |

\*N is the multiplier number.

Journal of Integrated Circuits and Systems 2015; v.10 / n.2:103-112

Figure 8. Layout - 100µm X 100µm - 180 nm CMOS Process

## **V. SIMULATIONS RESULTS**

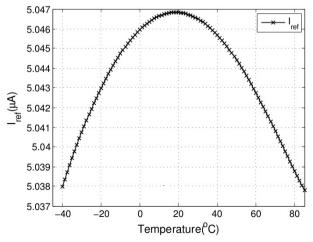

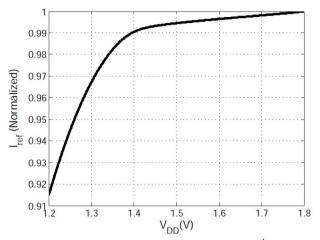

All results presented here were estimated using post-layout extracted parasitic. The circuit was designed to generate 5  $\mu$ A, and presents a slight curvature due to the nonlinearity of mobility thermal dependence [4], as shown in Fig. 9. The good thermal stability of reference is evident from -45 to +85°C in this Figure. Effective temperature coefficient ( $TC_{eff}$ ), as given by Eq. (47), is 15 ppm/°C, under  $V_{DD} = 1.8$  V. Power supply sensitivity resulted around 1%/V for a  $V_{DD}$  range of 1.4 to 1.8 V, as shown in Fig. 10.

$$TC_{eff} = \frac{I_{REE_{MAX}} - I_{REE_{MIN}}}{I_{REF}(T_0)(T_{MAX} - T_{MIN})}$$

(47)

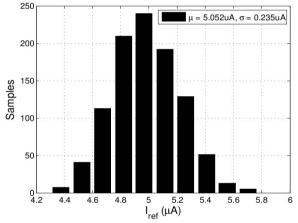

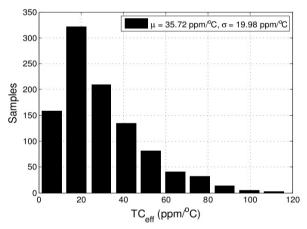

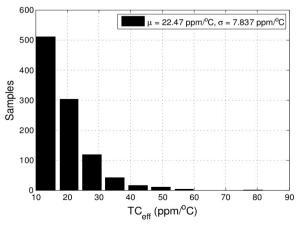

Since the impact of fabrication process is critical for performance repeatability of circuit, Monte Carlo

Figure 9. Current Reference vs. Temperature.

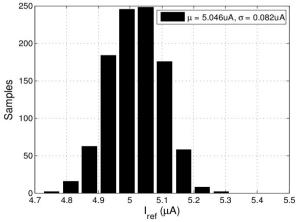

(MC) simulation was done separately only for local mismatch effects and for average process variations including mismatch, with 1000 runs each. For average process MC, all similar devices are changed in the same

Figure 10. Normalized Power Supply Sensitivity.  $\left(\frac{I_{REF}}{I_{REF}@V_{DD}=1.8}\right)$

**Figure 11.**  $I_{\rm REF}$  Monte Carlo simulation including process and mismatch.

Figure 12. I<sub>REF</sub> Monte Carlo simulation only for mismatch.

way for each run. For local mismatch MC, parameters of each transistor is changed individually for each run. Fig. 11 shows the reference current spread, with a  $\sigma/\mu$  = 4.5% for mean process variation + mismatch, while only local mismatch is shown in Fig. 12, and yields  $\sigma/\mu$  = 0.65%. From these simulations, one can conclude that average process variations (batch-to-batch) is the main yield reduction cause.

Fig. 13 presents the spread of effective temperature coefficient  $(TC_{eff})$  for average process variations and mismatch, where 98 % of parts yields a  $TC_{eff}$  below 100 ppm/°C. Fig. 14 presents the same spread but only for local mismatch, where all parts have  $TC_{eff} <$ 60 ppm/°C. Clearly, the factors, which are the major contributors to spread, are average process variations (batch-to-batch).

Table III presents a comparison of recently published current references. Clearly main advantages of our new topology are competitive area and low temperature coefficient.

Figure 13.  $\mathit{TC}_{\mathit{eff}}$  Monte Carlo simulation including process and mismatch.

Figure 14. TC<sub>eff</sub> Monte Carlo simulation only for mismatch.

| Specification           | This Work* | [6]* - I   | [6]* - II  | [2]**    | [8]*       | [9]*       | [3]**     | Unit   |

|-------------------------|------------|------------|------------|----------|------------|------------|-----------|--------|

| Technology              | 0.18       | 0.35       | 0.35       | 0.18     | 0.18       | 0.065      | 1.5       | μm     |

| Temperature             | -40 to 85  | -30 to 100 | -30 to 100 | 0 to 100 | -20 to 120 | -40 to 125 | -20 to 70 | °C     |

| Power Supply            | 1.4 - 1.8  | N/A        | N/A        | 1        | 2          | 3.3        | 1.2       | V      |

| I <sub>REF</sub>        | 5          | 15.1       | 13.65      | 144      | 263.5      | 6.45       | 0.0004    | μA     |

| Temperature Coefficient | 15         | 130        | 28         | 185      | 170        | 55         | 2500      | ppm/°C |

| Power                   | 342        | N/A        | N/A        | 227      | 80         | 155        | 0.002     | μW     |

| Area                    | 10000      | 4200       | 4200       | 315000   | N/A        | N/A        | 45000     | μm²    |

Table III. Comparison of CMOS Current References

#### **VI. CONCLUSION**

A new analytical approach for ZTC MOSFET condition was presented using an all-region model, since this effect could occur from moderate to strong inversion levels, depending on process characteristics. Simulation data from different threshold MOSFETs from three commercial processes (350, 180 and 130 nm, from 3 different foundries) shows that ZTC bias point is located from moderate to strong inversion, as predicted analytically. A self-biased CMOS current reference topology was also proposed and designed herein, based on MOSFET ZTC, composed by MOSFETs and one poly-silicon resistor. Proposed circuit was designed in a 180 nm process, for an average current of 5  $\mu$ A at room temperature under a power supply higher than 1.4 V. Post-layout simulation for typical device parameters resulted an effective temperature coefficient of 15 ppm/°C from -45 to +85°C, and a maximum of 100 ppm/°C for the same temperature range including process and mismatch variability effects. Monte Carlo simulations show a spread of  $\sigma/\mu = 4.5$  % for average process variation and mismatch  $\sigma/\mu = 0.64$  % only for local mismatch. Power consumption is  $342\mu$ W and silicon area taken by our circuit is just 0.010 mm<sup>2</sup>.

## ACKNOWLEDGEMENTS

This work was partially supported by CNPq, CAPES and by CI-Brasil Program.

#### REFERENCES

- H. Banba, H. Shiga, A. Umezawa, T. Tanzawa, and K. Atsumi, S. and Sakui. "A CMOS Bandgap Reference Circuit with sub-1-v operation". IEEE J. Solid-State Circuits, SC-6(1):2–7, Feb 1999.

- [2] A. Bendali and Y. Audet. "A 1-V CMOS Current Reference with temperature and process compensation". IEEE Trans. Circuits Syst., 54(2):1424–1429, 2007.

- [3] E. Camacho-Galeano, C. Galup-Montoro, and C. Schneider. "A 2-nw 1.1-V Self-Biased Current Reference in CMOS technology". IEEE Trans. Circuits Syst. II, 52(2):61–65, 2005.

- [4] I. Filanovsky and A. Allam. "Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS circuits". IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., 48(7):876–883, Jul. 2001.

- [5] I. Filanovsky, B. Bai, and B. Moore. "A CMOS voltage reference using compensation of mobility and threshold voltage temperature effects". 52nd IEEE International Midwest Symposium on Circuits and Systems, pages 29–32, Aug 2009.

- [6] F. Fiori and P. Crovetti. "A new compact temperature-compensated CMOS current reference". IEEE Trans. Circuits Syst. II, 52(11):724–728, 2005.

- [7] H. Klimach, T. Costa, S. Bampi, and C. Monteiro. "Resistorless switched capacitor bandgap voltage reference with low sensitivity to process variations". Electronics Letters, 49:1448–1449, 2013.

- [8] W. Liu and E. Kussener. "A resistor-free temperature-compensated CMOS current reference". Proceedings IEEE International Symposium on Circuits and Systems, pages 845–848, 2010.

- [9] M. Lukaszewicz, T. Borejko, and W. Pleskacz. "A resistorless current reference source for 65 nm cmos technology with low sensitivity to process, supply voltage and temperature variations". Proceedings IEE International Symposium on Design and Diagnostics of Eletronic Circuit and System, pages 75– 79, April 2011.

- [10] P. Malcovati, F. Maloberti, C. Fiocchi, and M. Pruzzi. "Curvature compensated BiCMOS bandgap with 1-v supply voltage". IEEE J. Solid- State Circuits, 36:1076–1081, July 2001.

- [11] C. Schneider and C. Galup-Montoro. CMOS Analog Design Using All-Region MOSFET Modeling. Cambridge University Press, 1st edition, 2010.

- [12] I. H. Semiconductor. http://www.investopedia.com/features/ industryhandbook/semiconductor.asp

- [13] M. Sze. Physics of Semiconductor Device. Wiley, 1981.

- [14] N. Talebbeydokhti, P. Hanumolu, P. Kurahashi, and U. Moon. "Constant transconductance bias circuit with an on-chip resistor". Proceedings IEEE International Symposium on Circuits and Systems, pages 2857–2860, May 2006.

- [15] MunEDA-Wicked. http://www.mos-ak.org/munich\_2013/presentations/02\_Matthias\_Sylvester\_MOS-AK\_Munich\_2013.pdf.

- [16] R. Widlar. "New developments in ic voltage regulators". IEEE J. Solid-State Circuits. 6(1):2–7, Feb 1971.

- [17] D. Wolpert and P. Ampadu. CMOS Analog Design Using All-Region MOSFET Modeling. Springer, 1st edition, 2012.

- [18] C. Yoo and J. Park. "CMOS current reference with supply and temperature compensation". Electronics Letters, 43(25), December 2007.

- [19] D. M. Colombo, G. Wirth, and S. Bampi, "Sub-1V band-gap based and MOS threshold-voltage based voltage references in 0.13µm CMOS," Analog Integrated Circuits and Signal Processing, vol. 82, no. 1, pp.25-37, 2015.

- [20] Boni, A., "Op-amps and startup circuits for CMOS bandgap references with near 1-V supply," Solid-State Circuits, IEEE Journal of , vol.37, no.10, pp.1339,1343, Oct 2002

- [21] Galup-Montoro, C.; Schneider, M.C.; Cunha, A.I.A.; de Sousa, F.Rangel; Klimach, H.; Siebel, O.F., "The Advanced Compact MOSFET (ACM) Model for Circuit Analysis and Design," Custom Integrated Circuits Conference, 2007. CICC '07. IEEE, vol., no., pp.519,526, 16-19 Sept. 2007