# STUDY: STOP ANISOTROPIC ETCHING IN OXIDE THERMALLY GROWN AIMING USE OF SOI WAFERS

# Mariana Amorim Fraga<sup>\*</sup>; Leandro Léo Koberstein<sup>\*\*</sup>; Edgar Charry and Humber Furlan

*Abstract* -The use of SOI (Silicon on insulator) formed by SIMOX (Separation by ion implantation of oxygen) is one of the most promising techniques for manufacture of silicon microsensors. SOI substrate has silicon top layer used as an active material with the excellent properties of the singlecrystaline silicon and buried oxide (SiO<sub>2</sub>) as a sacrificial layer. The study of the SiO<sub>2</sub>/Si interface is fundamental for define characteristics of the structures formed in this substrate.

*Index Terms* – BOX (buried oxide), oxide thermally grown, SiO<sub>2</sub>/Si interface, SOI.

#### I. INTRODUCTION

ILICON micromachining is very suitable for microsensors but some problems are still to be solved. The use of silicon on insulator (SOI) substrate is likely the best way to overcome these remaining difficulties. With this kind of substrate we can gather many advantages: microelectronic technology compatibility, batch process for anisotropic chemical etching, mechanical quality of single crystalline material, silicon superficial layer to realize either the transducer (strain gauges) or the surface microstructure and sacrificial layer electrically insulating and chemically selective<sup>[1]</sup>. This work study silicon wafer with SiO<sub>2</sub> thermally grown that during anisotropic etching in KOH solution (27 wt.% KOH /water solution and  $85^{\circ}C$  ) come across the SiO<sub>2</sub> how layer of stop . The experiments were realized in silicon wafer P type and 10-20  $\Omega$ .cm resistivity with SiO<sub>2</sub> thermally grown by fact of the SOI wafer to be very expensive for experiments of laboratory.

# II. FORMATION OF THE BURIED OXIDE (SiO2)

Two steps are necessary to manufacture a SIMOX structure: a deep ion implantation of oxygen followed by a high temperature annealing the commonly used dose  $1.8 \times 10^{18}$  ions of oxygen/cm<sup>2</sup> and 50 to 225 KeV of energy.

The implantation must be done at a temperature higher than  $500^{\circ}$ C to avoid the amorphization of the substrate. The very high temperature annealing (>1300°C) allows the elimination of the defects created during the

#### \*maf@lsi.usp.br

Laboratório de sistemas Integráveis Escola Politécnica da USP Eng. Elétrica São Paulo – SP – Brasil \*\*<u>kobers@lsi.usp.br</u> Faculdade de Tecnologia de São Paulo Mecânica de Precisão São Paulo – SP - Brasil implantation process and a complete dissolution of all  $precipitates^{[1,2]}$ .

# III. EXPERIMENTAL

#### - Choice of the wafer

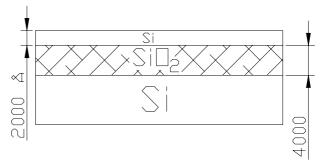

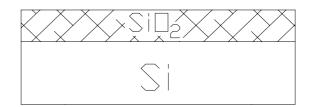

The main objective of the work is show the importance  $SiO_2$  layer in SOI wafer. A silicon wafer with  $SiO_2$  thermally grown was selected by the fact of the oxide grown in surface present similar characteristics of the BOX (buried oxide). This make possible characterize  $SiO_2$  / Si interface of SOI wafers (figure 1) using Silicon wafer with oxide thermally grown (figure 2).

Fig. 1. SOI wafer.

Fig. 2. Silicon with oxide thermally grown wafer.

b - Stop anisotropic etching

The wafer with oxide thermally grown was placed in KOH solution for anisotropic etching. Anisotropic etching is the reaction between silicon and hidroxila. Conform reaction<sup>[3]</sup>.

$$Si + 2OH^{-} + H_2O \rightarrow SiO_3^{-2} + 2H_{2(g)} + 0.8693V$$

(1)

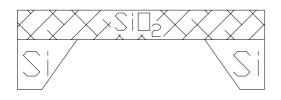

The process of etching remain 3 hours. After etching was possible identify the  $SiO_2/Si$  interface using optic microscope and Scanning Eletronics Microscope (SEM). The visualization is possible by  $SiO_2$  present a low etch rate when in the KOH (figure 3).

Fig. 3. Silicon with oxide thermally grown wafer after anisotropic ecthing.

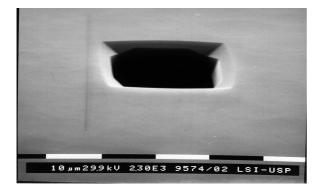

Structures analysed after anisotropic etching present some deffects (figure 4). The defects are resulted of meet between the (111) silicon surfaces and the SiO<sub>2</sub>. This happen by the fact of KOH search the plan (111) by the side of SiO<sub>2</sub> altering the region of meet of surfaces. Study detailed are being realized.

Fig. 4. Structures with deffects.

## IV. INTERFACE Si/SiO2

Numerous studies have been performed in order to elucidade the nature of the  $Si/SiO_2$ . These studies have investigated the following interface characteristics: a) the special location of the interface traps and the oxide fixed charge; b) the morphology of the boundary; c) the chemical composition of the  $SiO_2$  near the boundary; and d) the width of the interface<sup>[4]</sup>. The interfacial region consisting of single crystal silicon followed by monolayer in which there is some  $SiO_2$ ,  $Si_2O_2$  and  $Si_2O$ . There are four types of charge in the oxide or near the  $SiO_2/Si$  interface: interface trap charge, fixed oxide charge, mobile ionic charge and bulk oxide trapped charge.

## V. CONCLUSIONS

The use of stop anisotropic etching in silicon wafer with oxide thermally grown allow characterizer  $SiO_2/Si$  interface. The properties of buried oxide are similar the of thermally grown. This show that the process of stop anisotropic etching is a form efficient and economic of study the characteristics SOI wafer. The study of this characteristics are important for analysis of microstructures formed.

#### VI. REFERENCES

[1] B.Diem, P. Rey, S.Renard, S. Viollet Bosson, H.Bono, F. Michel, M.T. Delaye and G.Delapierre, SOI 'SIMOX'; from bulk to surface micromachining, a new age for silicon sensors and actuators, Sensors and Actuators A 46-47 (1995) 8-16.

[2] A. Ogura and H. Ono, Evaluation of buried oxide formation in lowdose SIMOX process, Applied Surface Science 159-160 (2000) 104-110.

[3] Furlan, Humber- Proposta de implementação de membranas em sensores de pressão a elementos piezoresistivos utilizando a técnica de pós-processamento. São Paulo, 1997.

[4] Wolf, Stanley. "Silicon Processing Vol. 2"for the VLSI ERA, 1990 Lattice Press.