# Fabrication and Electrical Characterization of NMOSFET Transistors

Michele Rodrigues\*, A. S. Nicolett, M. A. Pavanello, J. A. Martino, Jean Louis Noullet<sup>1</sup>

Laboratório de Sistemas Integráveis Escola Politécnica da Universidade de São Paulo Av.Prof. Luciano Gualberto, trav. 3 nº 158 CEP 05508-900 – São Paulo – Brazil <sup>\*</sup>e-mail: moa.mi@uol.com.br <sup>1</sup>AIME – Atelier Interuniversitaire de Microelectronique, Toulousse, France

Abstract—This work presents an electrical characterization of NMOSFETs devices processed in an Interuniversity Center. The  $I_D \ge V_G$  and  $I_D \ge V_D$  curves were used to extract electrical parameters. The results were compared to literature and a good agreement was found.

### I. INTRODUCTION

$T^{\rm HE}$  devices used in this work were processed at AIME – Atelier Interuniversitaire of Microelectronique, Toulousse, France.

The processed wafers have different NMOS circuits and devices such as diodes, capacitors, transistors and resistors. In this work just NMOS transistors were used in the electrical characterization.

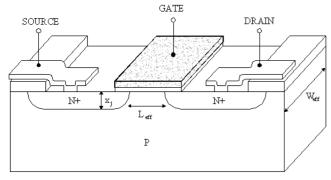

Figure 1 shows the long and short channel NMOS transistors used. The experimental results are presented in the Section III.

Figure 1: a) Long channel NMOS transistor; b) Short channel NMOS transistor .

\*Corresponding author. Tel.: +55-11-30919737; fax: +55-11-30915665. E-mail address: moa.mi@uol.com.br (Michele Rodrigues).

## II. PROCESS DESCRIPTION

The goal of the process was to build NMOSFET transistors using polysilicon gate and the P-type substrate. The first step was to deposit a layer of  $SiO_2$  to realize the first photolithography where the active regions were defined.

The gate oxide was grown in a temperature about 1100 °C and after this, a layer of polysilicon doped with Phosphor was deposited using a LPCVD reactor (Low Pressure Chemical Vapor Deposition). The next stage (photolithography n° 2) defined the location of the source, drain and the channel lengths. Two different mask channel lengths were used ( $L_m$  equal 6 and 18µm) and a mask channel width of  $W_m = 180\mu m$ .

Source and drain regions were formed by Phosphor diffusion at 1050 °C during 15 minutes followed by an annealing of 10 minutes at 1100 °C. Due to the lateral diffusion of the source and drain regions, there was a reduction in the mask channel length. A resistivity of 0.00117  $\Omega$ .cm was obtained in the source and drain regions by four probe measurements.

A SiO<sub>2</sub> L.T.O. (Low Temperature Oxidation) layer of 500 nm was deposited on the whole wafer and placed in a oven (420°C) to the accomplishment of the photolithography n° 3, that has the objective of open the contacts.

A 500 nm layer of aluminum was evaporated using Vacuum Thermal Method to realize the last photolithography that delineated the interconnections of the components with the metal. To finish the process an annealing of the metal in a temperature about 400 °C, during 20 minutes, was realized.

#### **III. EXPERIMENTAL RESULTS**

After the process, the short channel NMOSFET devices presented an effective channel lengths  $L_{eff}$  of 3.17 $\mu$ m, an effective channel doping concentration Na =  $9x10^{15}$  cm<sup>-3</sup>, front gate oxide thickness t<sub>ox</sub> of about 68.3nm and a junction depth  $x_i$  of 1.6  $\mu$ m.

Figure 2 shows a cross-section of the devices where some used notations are illustrated.

Figure 2: Cross-section of the NMOSFET device where some used notations are illustrated .

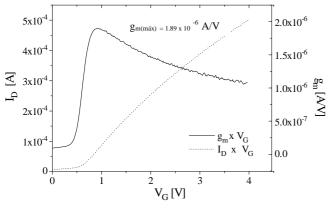

The  $I_D \ x \ V_G$  and  $I_D \ x \ V_D$  curves were used to extract some parameters, such as threshold voltage  $V_{th}$ , Early Voltage  $V_{EA}$  and the transconductance  $g_m$ . All measurements were performed using a HP4145B Semiconductor Parameter Analyzer. Figure 3 shows the  $I_D \ x \ V_G$  and  $g_m \ x \ V_G$  curves with  $V_D = 0.1 V.$

Figure 3:  $I_D x V_G$  and  $g_m x V_G$  curves.

The Linear Extrapolation Method was used to extract the threshold voltage resulting  $V_{th} = 0.53V$ . To find the transconductance, equation (1) was derived as a function of  $V_G$  resulting equation (2).

$$I_{D} = \mu \cdot Cox \cdot \frac{W}{L} \left[ \left( V_{G} - V_{th} \right) \cdot V_{D} - \frac{V_{D}^{2}}{2} \right]$$

(1)

$$g_{\rm m} = \mu \cdot \operatorname{Cox} \cdot \frac{W}{L} \cdot V_{\rm D}$$

<sup>(2)</sup>

Where  $\mu$  is the mobility,  $C_{ox}$  is the gate oxide capacitance, W the channel width, L is the channel length,  $V_D$  is the drain voltage,  $V_{th}$  is the threshold voltage,  $V_G$  is the gate voltage and  $g_m$  is the transconductance. The transconductance is linearly related to the mobility and one can monitor the mobility evolution due to the gate bias increase by measurements  $g_m$ . From figure 3 there is a reduction of  $g_m$  for  $V_G$  larger than 1 V caused by the mobility degradation due to vertical electrical field, as the drain voltage is small.

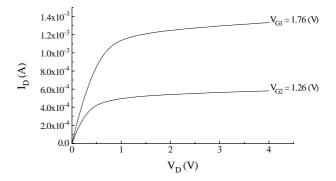

Figure 4 shows  $I_D \ge V_D$  curves for different  $V_G$ . The Early Voltage was extracted from figure 4 resulting  $V_{EA} = -22 \text{ V}$ .

Figure 4: I<sub>D</sub> x V<sub>D</sub> curves for different V<sub>G</sub>.

## IV. CONCLUSION

This work has presented a process description of NMOSFETs devices built at AIME – Atelier Interuniversitaire of Microelectronique, Toulousse, France.

An electrical characterization was performed and a threshold voltage  $V_{th} = 0.53V$  and Early Voltage  $V_{EA} = -22$  V were obtained.

#### REFERENCES

- M. A. Pavanello, J. A. Martino, Denis Flandre, "Graded-channel Fully depleted Silicon-On-Insulator nMOSFET for resucing the parasitic bipolar effects," 2000.

- [2] Sedra, Adel S.; Smith, Kenneth, C., "Microeletronic", 4nd ed., Ed. Makron Books, 2000, pp. 328-364.

- [3] Streetman, Bem G., Solid State electronic devices/Ben G. Streetman -4 th - ed., Prince Hall do Brazil Ltda, Rio de Janeiro, 1995, pp. 130-182.