# Simulation and measurements of asymmetrical delay elements: a study in temperature and supply voltage.

Martín Bremermann, Joel Gak, Alfredo Arnaud

Dep.Ingeniería Eléctrica, Universidad Católica del Uruguay

8 de Octubre 2738/DIE Montevideo Uruguay - CP.11600. Contact email: mbremerm@ucu.edu.uy

#### ABSTRACT

The time delay of a chain of asymmetrical inverters is analyzed with both measurements and simulations. Delay variations with temperature and supply voltage are investigated. Asymmetrical inverters demonstrate to be much less sensitive to supply voltage voltage, and less sensitive to temperature.

### **1. INTRODUCTION**

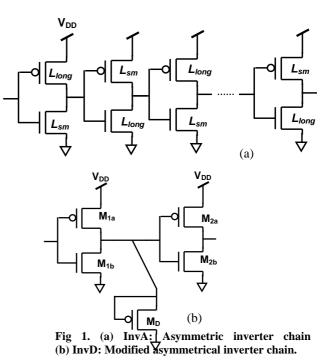

Several integrated systems require the implementation of a constant time delay that does not change too much with temperature, supply voltage, or technology parameters. Untrimmed delay elements however present fluctuations, like usual R-C networks, or classic inverter chains for example. Novel topologies have been proposed in the past to overcome the problem [1,2], and the time delay of inverter chains has been investigated in detail[3]. An asymmetric inverter chain like the one in Fig.1(a), alternate small transistors sized  $W_{sm}$ ,  $L_{sm}$  with very long ones sized  $W_{sm}$ ,  $L_{long}$ ;  $L_{long} >> L_{sm}$ . The resulting delay is much different for the rising, and falling edge, of the input signal. The large delay -when long transistors have to charge/discharge large capacitors- is little sensitive to technology parameters [1]. The asymmetric inverter in Fig.1(b) incorporates a

PMOS transistor connected to ground. This transistor  $M_D$  presents not only an extra capacitance to  $M_1$ , but also it opposes to  $M_{1a}$ when charging  $M_2$  gate capacitance. The effect helps to compensate time delay variations related to supply voltage. In this paper three previously fabricated delay elements are compared:

<u>Classical Inverter (named InvC)</u>: is a chain of 8 classic inverters with both PMOS and NMOS transistors sized  $W / L = 4/160 \mu m$ .

<u>Asymmetrical Inverter (named InvA)</u>: is a chain of 2 inverters like in Fig.1(a) with  $W_{sm} = 4\mu$ m,  $L_{sm} = 2.4\mu$ m,  $L_{long} = 480\mu$ m.

<u>Modified inverter (named InvD)</u>: is the inverter of Fig.1(b) with  $W_{sm} = 4\mu$ m,  $L_{sm} = 2.4\mu$ m,  $L_{long} = 280\mu$ m,  $L_D = 480\mu$ m.

All the inverters incorporate input and output buffers. In the following sections, detailed time delay simulations and measurements will be presented for this three circuits while varying the temperature (-10 to  $80^{\circ}$ C) and supply voltage (1.5 to 5V).

#### 2. SIMULATIONS AND MEASUREMENTS

The integrated circuit was fabricated in a standard 0,8um CMOS technology. The work was divided into two stages.

In the first stage we varied the voltage supply between 0.9V and 5.0V in steps of 0.1 $\pm$ 10mV. The procedure that we follow to test it was as follows: first we generated a 1kHz square wave with a WAVETEK FG2C function generator (into 50 $\Omega$  load). Note that the main thing to bear in mind was that te supplied voltage had to be the same as the amplitude of the square wave. We used a digital oscilloscope (Tektronix TDS1002) to measure the delay t<sub>d</sub> of the outcoming signal from the IC of each of the inversors. This procedure was repeated for each voltage. To reduce some glitches at the transistion time we used a tantalum capacitor between V<sub>DD</sub> and V<sub>SS</sub>. The results of this stage is shown in Fig. 2(a).

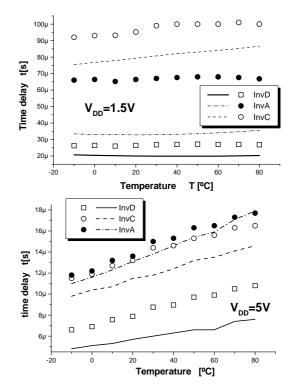

In stage two we varied not only the voltage but the temperature as well. In this case the voltage at which the IC was tested was: 1.5V, 3.0V, 4.0V and 5.0V for each temperature. The range of temperatures went from  $-10^{\circ}$ C to  $80^{\circ}$ C in  $10^{\circ}$  steps. In this stage we used the same measurement techniques as we did in stage one however now the circuit was put into an oven which is used for investigation purpouses only and its tested range goes from

$-100^{\circ}$ C to  $120^{\circ}$ C. To measure the oven's temperature it was used a digital thermometer (VOLTCRAFT 502). It has a thermocouple type K and its temperature range goes from  $-200^{\circ}C\pm0.1^{\circ}C$  up to 1370°C. The mesurements were made at 1KHz. The results of this stage is shown in Fig. 2(b).

The program we used to simulate was SMASH 5.2.2. The simulation model was Bsim 3V3 for standard CMOS 0.8µm technology, typicall model.

#### **3. CONCLUSIONS**

The asymmetrical inverter chains behave better than classic one, because are less sensitivo to changes on the supply voltage. The modified one InvD also shows a point with a null derivative respect to  $V_{\rm DD}$ . The three inverters show a similar behaviour with temperature, however for low supply voltages asymmetrical inverters show a negligible delay variation from -10 to 80°C. Asymmetrical inverters enable to build more stable circuits under any of the given circunstances.

## 4. ACKNOWLEDGMENTS

The authors would like to thank Prof.Conrado Rossi, and the Microelectronics Group at Universidad de la República for helpful suggestions and circuit samples.

## 5. REFERENCES

- A.Arnaud, C.Rossi, "Análisis de una cadena de inversores asimétricos como elemento de retardo", Procs.VII Workshop de Iberchip, Montevideo, March 2001.

- [2] G.Kim, M.Kim, B.Chang, W.Kim, "A Low-Voltage, Low-Power CMOS Delay Element", IEEE-JSSC, Vol.31, N°7, Jul.1996.

- [3] S.Dutta, S.Mahant Shett, S.L.Lusky, "A Comprehensive Delay Model for CMOS Inverters", IEEE-JSSC, Vol.30, N°8, Aug.1995.

Fig 2. (a) Measured (scatter), and simulated (line) time delay  $t_d$  against supply voltage at room temp.

**(b)** Normalized sensitivity  $NS = \frac{\partial t_d}{t_d \partial V_{DD}}$

Fig 3. Time delay against temperature for InvA, InvC,InvD, at  $V_{DD}$ =1.5V(up) and  $V_{DD}$ =5V (bottom).