# **Techniques of Parameters Extraction in SOI – MOSFET Devices**

Artur Gasparetto Paiola, Marcelo Antonio Pavanello and João Antonio Martino Integrated Systems Laboratory - Polytechnic School - University of São Paulo

## I. INTRODUCTION

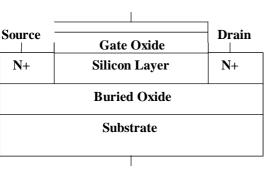

The SOI-MOSFET device is a transistor with an insulated layer between the channel region and the substrate. Figure 1 illustrates the cross section of an SOI-MOSFET.

**Front Gate**

Back Gate

Figure 1: SOI-MOSFET cross section.

As like in bulk MOSFET, the SOI-MOSFET devices transistors has electrical characteristics that can be extracted using some common techniques between them.

### II. THRESHOLD VOLTAGE EXTRACTION

In fully depleted SOI-MOSFET transistor there are interaction between first and second interfaces. The applied voltage in the first gate ( $V_{G1}$ ) will influence the bias conditions at the second gate ( $V_{G2}$ ), and vice-versa.

$$V_{G1} = \phi_{MS} - \frac{Q_{oxl}}{C_{oxl}} + \left(1 + \frac{C_{si}}{C_{oxl}}\right) \phi_{S1} - \frac{C_{si}}{C_{oxl}} \phi_{S2} - \frac{0.5Q_{depl} + Q_{inil}}{C_{oxl}} \quad (1)$$

$$V_{G2} = \phi_{MS2} - \frac{Q_{ox2}}{C_{ox2}} + \left(1 + \frac{C_{si}}{C_{ox2}}\right) \phi_{S2} - \frac{C_{si}}{C_{ox2}} \phi_{S1} - \frac{0.5Q_{depl} + Q_{S2}}{C_{ox2}} \quad (2)$$

where:  $V_{G1}$  and  $V_{G2}$  = front and back gate voltage respectively;  $\varphi_{MS1}$  and  $\varphi_{MS2}$  = front and back work function difference respectively;  $Q_{ox1}$  and  $Q_{ox2}$  = fixed charge density at front and back interface respectively;  $C_{ox1}$  and  $C_{ox2}$  = front and back gate oxide capacitance respectively;  $C_{si}$  = silicon capacitance;  $\varphi_{S1}$  and  $\varphi_{S2}$  = potential in front and back interface respectively;  $Q_{depl}$  = depletion charge in silicon film; Qinv1 = inversion charge at front interface;  $Q_{S2}$  = surface charge at back interface.

The equations (1) and (2) above show the relationship between the front gate voltage and the surface potentials, and the interdependence of values in the FD SOI-MOSFET.

With the combination of equations (1) and (2) it is possible to describe the threshold voltage (Vth) expression at front interface, with depleted back interface, in the equation (3).

$$Vth_{depl2} = Vth_{acc2} - \frac{C_{si}C_{ox}}{C_{oxl}(C_{si} + C_{ox2})} (V_G - V_{g2})$$

(3)

where:  $Vth_{depl2}$  = threshold voltage with depleted back interface;  $Vth_{acc2}$  = threshold voltage with accumulated back interface;  $V_G$  = gate voltage.

But, the most used method to get the threshold voltage is using an  $I_{DS} \times V_{GS}$  experimental curve in linear regime.

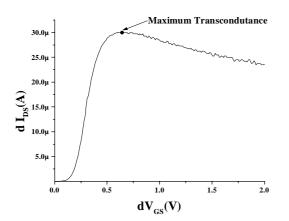

Doing the double differentiate curve of the  $I_{DS} \times V_{GS}$  curve will obtain a graph like figure 2.

Figure 2: Double differentiate  $I_{DS} \times V_{GS}$  curve, with the maximum positive peak indicating the correspondent threshold voltage value.

The maximum positive peak pointed corresponds to the threshold voltage value. As can be seen in figure 2, there is an excess of noise in the second derivative curve and, sometimes, it is necessary to use a fast Fourier transformer filtering to reduce it.

#### III. TRANSCONDUCTANCE EXTRACTION

The transconductance (Gm) is a measure of the effectiveness of the control of the drain current ( $I_{DS}$ ) by the gate voltage ( $V_{GS}$ ).

In thin film fully depleted SOI-MOSFET devices the transconductance can be calculated by the following equation:

$$Gm = \frac{W\mu_n C_{ox1}}{L(1+\alpha)} (V_{G1} - Vth)$$

<sup>(4)</sup>

where: W = channel width;  $\mu_n$  = electrons mobility in inversion layer; L = channel length;  $\alpha$  represents the net capacitance of the SOI MOSFET.

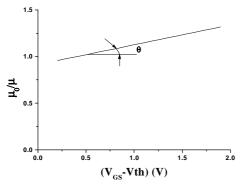

As for the threshold voltage, the transconductance also can be extracted from an  $I_{DS} \times V_{GS}$  curve, but in this case, a single differentiate one. According to equation (5), Gm is directly proportional to the mobility

Thus, the figure 3 shows the point of maximum transconductance, which also means the maximum carrier mobility.

Figure 3: Single differentiate  $I_{DS} \times V_{GS}$  curve, showing the maximum transconductance point, where carriers mobility is maximum.

Increasing  $V_{GS}$  higher than the maximum transconductance point, there is degradation in the carriers mobility due to the transversal electric field.

The mobility degradation is given by the equation:

$$\mu = \frac{\mu_0}{1 + \theta \left( V_{GS} - Vth \right)} \tag{5}$$

where:  $\mu =$  carriers mobility at  $V_{GS};$   $\mu_{0} =$  maximum carriers mobility;  $\theta =$  mobility degradation coefficient.

The  $\theta$  coefficient is obtained using the curve  $\mu/\mu_0 \ge V_{GS}$ -Vth as seen in the figure 4.

Figure 4: Experimental graph demonstrating the mobility degradation coefficient.

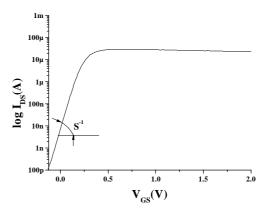

IV. SUBTHRESHOLD SLOPE EXTRACTION The subthreshold slope is defined as:

$$S = \frac{dV_G}{d(\log I_D)} = \frac{kT}{q} \ln(10) \left(\frac{1+C_{SiD}}{C_{ox}}\right)$$

(6)

where: k= Boltzmann constant; T = temperature;  $C_{\text{SiD}}$  = is the silicon film capacitance.

The figure 5 demonstrate the experimental curve log  $I_{DS} \times V_{GS}$  to extract the subthreshold slope, where the calculated and experimental values are very close: 0,0720 (V/dec) and 0,07 (V/dec) respectively.

Figure 5: Log IDS x VGS curve, indicating how the slope is measured.

## V. SERIES RESISTANCE EXTRACTION

A MOSFET transistor is considered an association with a transistor and two series resistances. This kind of resistance can diminish the performance of the device and circuit which transistor is connected. This problem is especially important for SOI transistors due to its thin silicon layer

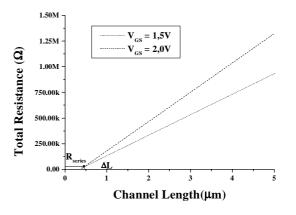

Calculating the R<sub>tot</sub> (Total Resistance) from the I<sub>DS</sub> x V<sub>GS</sub> curve using Ohm's Law and plotting them in a graph in function of the channel length, with different V<sub>GS</sub> values, these lines will intercept in a defined point coordinate called R<sub>series</sub> x  $\Delta L$  (Series Resistance x Effective Length Channel) like seen in the figure 6.

Figure 6: Total Resistance x Channel Length graph with a group of  $V_{GS}$  curves; the point of intersection gives the Rserial and  $\Delta L$ .

The SOI-MOSFET devices used to extract the series resistance were simulated using the MEDICI program. The transistors were 1, 2, 3 and 5µm channel lengths and the respective values to  $R_{series}$  and  $\Delta L$  are: 28,7K $\Omega$  and 0,46µm.

## VI. CONCLUSION

This paper presented and discussed some electrical parameters extraction methods conventionally used in bulk MOSFETs applied to thin film SOI transistors. The models support the use of the presented methods for fully depleted SOI-MOSFETs.

## VII. ACKNOWLEDGMENT I would like to thanks FAPESP for its financial help.

### VIII. REFERENCES

[1] Jean – Pierre Colinge, "Silicon – On – Insulator Technology",

[2] A. S. Nicollet, "Estudo da Resistência Série e do Comprimento Efetivo de Canal em Transistores MOS Convencionais e SOI MOS", M.S. Thesis, Department of Electronics Engineering – LSI – USP, São Paulo, Brazil.

[3] M. A. Pavanello, "Influência do Substrato no Transistor SOI MOSFET em Temperatura Ambiente (300K) e em Baixa Temperatura (77K)", M.S. Thesis, Department of Electronics Engineering – LSI – USP, São Paulo, Brazil.