## STUDY OF SIMULATION MOBILITY MODELS FOR ELECTRONIC DEVICES

André Luiz Perin<sup>1</sup>, Paula Ghedini Der Agopian<sup>1</sup>, Renato Camargo Giacomini<sup>1,2</sup>

1 Centro Universitário da FEI

2 Universidade São Judas Tadeu

# ABSTRACT

Numeric device simulation becomes each time more essential for technologic evolution, as it permits previous evaluation between incremental geometric and parametric variations before device implementation. The possibility of observing internal physical variables such electric potential and charge distribution confronted to the terminal current-voltage results, allows a better understanding of physical phenomena, and therefore contributes significantly to technologic evolution. In the present preliminary study, an exploration of some mobility models is shown for a SOI nMOS transistor. The default parameters are firstly adopted and then some mobility model parameters of ATLAS device simulator are changed for comparison.

## 1. Introduction

Today, numerical simulation has been used as a complementary tool in order to better understand the influence of the downsizing, geometry variation and new materials on devices behavior.

Numerical methods usually consider the studied object as a set of points, or nodes, called grid and the simulator equations are numerically solved for each node.

The simulation framework allows mathematical modeling of electronic devices from physical models, empirical models and a mix of both. Physical models use a set of differential equations, derived from Maxwell's and other well known laws. Empirical models can be applied only to some aspects of devices behavior as mobility degradation and recombination statistics. In most cases, it is necessary to use both types of models in order to get useful information.

One of the most interesting issues of semiconductors technology is the electrons and holes mobility. As defined by Colinge [1], mobility is proportional to the relaxation time of the electrons and inversely proportional to their effective mass. The drift velocity of electrons in an electric field can be shortened to the following expression:

$$v_{dn} = -\frac{q\,\tau_n}{m_e^*} \mathcal{E} = -\mu_n \mathcal{E} \tag{1}$$

where q is the electron charge,  $\tau_n$  is the relaxation time of the electrons,  $m_e^*$  is the effective mass of the electron,  $\mu_n$  is the electron mobility,  $v_{dn}$  is the average drift velocity and  $\varepsilon$  is the electric field.

The electron mobility  $(\mu_n)$  can be expressed, in a very short description, by the average drift velocity  $(v_{dn})$  of an electron divided by an electric field ( $\epsilon$ ), as seen in Equation 2 [1]:

$$\mu_n = -\frac{v_{dn}}{\varepsilon} = \frac{q \tau_n}{m_{\rho}^*}$$

(2)

Since mobility is proportional to the relaxation time it decreases with temperature increase because thermal lattice vibrations increase with temperature. Similarly, impurities and defects cause electron scattering (collisions), and therefore, mobility decreases with increasing impurity or defect concentration.

In this work a comparative study of the mobility models implemented in ATLAS is presented. For this analysis the Silicon-On-Insulator (SOI) technology was chosen. The SOI MOSFET device is similar to a conventional MOSFET device, except for buried oxide layer under the active region. This design improves the SOI MOSFET electrical behavior; as it prevents most of the parasitic effects seem in bulk silicon devices [2].

## 2. METHODS AND MODELS

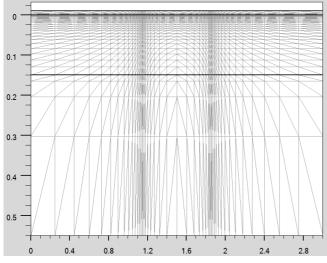

The SOI device used in all simulations, as represented in Figure 1, is an n-channel MOS transistor with 150 nm of silicon layer over 400 nm buried oxide and a 10 nm of gate oxide thickness. Figure 1 shows the grid of the simulated device as it was defined in ATLAS simulator.

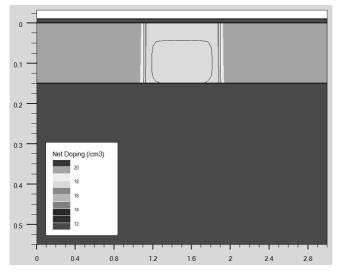

The substrate doping concentration (p-type) was considered uniform with  $2x10^{17}$  cm<sup>-3</sup> and at source and drain (n-type) the doping concentration is a Gaussian distribution with a peak of  $1x10^{20}$  cm<sup>-3</sup>. The channel length is 0.735  $\mu$ m. It was defined the interface charges of  $3x10^{10}$  cm<sup>-2</sup> at the first interface and  $1x10^{11}$  cm<sup>-2</sup> at the second one.

The net doping concentration of the defined device is shown on Figure 2.

This device was the same for all of the simulations executed when only the mobility models were changed.

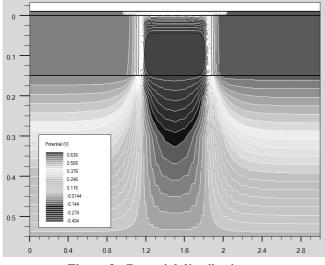

Figure 3 shows the potential distribution on the studied device biased in triode with 50 mV between source and drain and 1V applied to the gate contact.

Figure 1 - Grid of the simulated SOI device

Figure 2 - Net doping concentration and depletion region

Figure 3 - Potential distribution

For this study the following mobility models available were evaluated. They were: Constant Low Field Mobility Model, Analytic Low Field Mobility Model, Arora Model, Masetti Model, Conwell-Weisskopf Model, Brooks-Herring Model, Klaassen's Unified Low Field Mobility Model and the Shirahata's Mobility Model [3].

#### Constant Low Field Mobility Model

This model calculates the low field mobility as a constant in each region of the simulated device and doesn't consider the doping concentration, carrier density and electric field. It does account the effects of the temperature.

#### Analytic Low Field Mobility Model

This model was developed based upon the work of Caughey and Thomas [4] can be used to specify low-field mobility with the influence of doping and temperature for both, electron and hole.

#### Arora Model for Low Field Mobility

This is another analytic model for the doping and temperature dependence of the low field mobility available. This model consider the total doping concentration, lattice temperature, for both electron and hole mobilities [5].

#### Masetti Model For Low Field Mobility

The dependence of mobility on carrier concentration over a range of 8 orders of magnitude in carrier concentration from approximately  $10^{13}$  cm<sup>-3</sup> to  $10^{21}$  cm<sup>-3</sup>[6]. This model provides a set of parameters for Arsenic and Phosphorous n-doped Silicon. The model is optimized for room temperature.

#### Conwell-Weisskopf Model

This model is an adaptation of Conwell-Weisskopf theory to carrier-carrier scattering which must be used with another low field mobility model. It considers the effects of temperature, electron concentration and hole concentration in addition to the effects of carrier-carrier scattering.

## Brooks-Herring Model

Like the Conwell-Weisskopf model, this model adds in the effects of carrier-carrier scattering to the low field mobility using Matthiesen's rule as follows:

$$\frac{1}{\mu_n} = \frac{1}{\mu_{n0}} + \frac{1}{\mu_{nCCS}}$$

(3)

#### Klaassen's Unified Low Field Mobility Model

This model provides a unified description of majority and minority carrier mobilities. It includes the effects of lattice scattering, impurity scattering, carrier-carrier scattering, and impurity clustering effects at high concentration [7]. The model is effective under some circumstances like the temperature range over 70 K and 500 K, minority hole mobility as a function of donor concentration from  $10^{17}$ cm<sup>-3</sup> to  $10^{20}$  cm<sup>-3</sup>, minority electron mobility as a function of acceptor concentration over the range of  $10^{17}$  cm<sup>-3</sup> to  $10^{20}$  cm<sup>-3</sup> and majority electron mobility as a function of donor concentration over the range of  $10^{14}$  cm<sup>-3</sup> to  $10^{22}$ cm<sup>-3</sup>.

### Shirahata Mobility Model

The Shirahata Mobility Model [8] is a general purpose MOS mobility model that takes into account screening effects in the inversion layer and perpendicular field dependence for thin gate oxides. This model is a combination of portions of Klaassen's model for low field mobility contributions and an empirically fit expression for the perpendicular field dependent mobility in the inversion layer.

The transconductances were generated from the drain current graphs by performing simple derivative calculations on the drain current data set, without smoothing.

The threshold voltages are result of the second derivative of the drain current function.

The derivative at a point is computed by taking the average of the slopes between the point and its two closest neighbors.

## **3. RESULTS AND DISCUSSION**

The following results were reached after models, grid and drain current steps definition. The models were defined with their default values. Most of studied models have parameters that could be adjusted to fit the curves to experimental results.

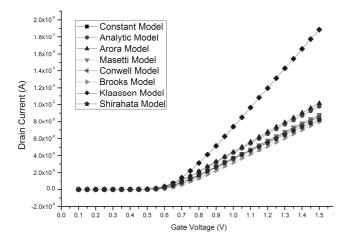

Figure 4 shows that most models present close drain currents  $(I_{DS})$  using the default parameters for the described device, except Klaassen's model that shows higher current levels since it starts with a higher initial mobility for electron, that should be adjusted by comparison with experimental data.

Figure 4 - Drain currents for all models

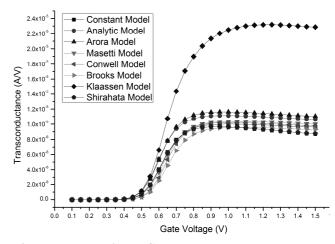

Figure 5 shows the obtained transconductances. The MOS transistor transconductance reflects the mobility as shown by Martino [9] since a low bias was applied to  $V_{DS}$  as shown in the following expression

$$\mu_n = \frac{L}{W.C_{OX}.V_{DS}}.g_m \tag{4}$$

were L is the channel length, W is the channel width,  $C_{OX}$  is the gate oxide capacitance,  $V_{DS}$  is the gate-to-source bias and  $g_m$  is the transconductance.

Figure 5 - Numerically Calculated Transconductance

The Table 1 shows the maximum threshold voltage value which was reached between 0.6V and 0.65Vin for all simulated models. These values were obtained by second derivative of drain current method [10].

| Model     | Threshold<br>Voltage (V) |

|-----------|--------------------------|

| Constant  | 0.60                     |

| Analytic  | 0.60                     |

| Arora     | 0.60                     |

| Masetti   | 0.60                     |

| Conwell   | 0.65                     |

| Brooks    | 0.65                     |

| Klaassen  | 0.65                     |

| Shirahata | 0.65                     |

Table 1 - Maximum Threshold Voltages

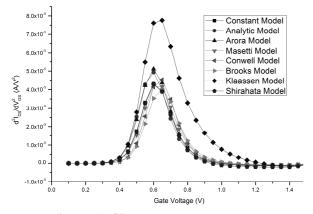

The threshold voltage plotted curve was quite different, as well as conductance curve, for Klaassen's model as shown in Figure 6.

Figure 6 – Simulated Threshold Voltages

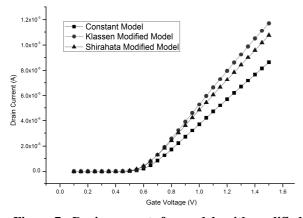

As a learning exercise, some adjustments have been made to Klaassen's and Shirahata's models to get closer results to a reference curve considered (Constant mobility model) as shown on Figure 7. The possibility of such adjustments makes possible the fitting work when experimental data are used as reference for device simulation.

Figure 7 - Drain currents for models with modified parameters

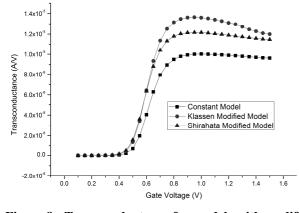

The transconductance curves behavior have also been modified and a mobility degradation could be seen on Klaassen's and Shirahata's models, as the plotted curves go down as the bias were increased, as shown on Figure 8

Figure 8 - Transconductance for models with modified parameters

#### 4. CONCLUSION

Most of studied low field mobility models take into account only the influence of temperature and doping concentration on mobility, which provides less accurate but fast simulation and allows preliminary device description adjustments and analysis. More complete models, like Klaassen's and Shirahata's, or some allowed model combinations give results that can better fit the experimental curves, once the transconductance and current curves may be almost completely adapted. The present preliminary work showed some of these possibilities. Future work will focus on a deeper exploitation of mobility models, especially for threedimensional devices, and will include adjustments to experimental data from measured devices.

#### **10. REFERENCES**

[1] Colinge, J.P. and Colinge C.A., Physics of Semiconductor Devices, Springer Verlag, NY, 2002

[2] Colinge, J.P., Silicon-On\_Insulator Technology: Materials to VLSI, Kuwler Academic Publishers, NY, 2002

[3] Atlas Device Simulator User's Manual, v. 5.10.0.R, Silvaco Int. Santa Clara, CA (USA), 2008.

[4] Caughey, D.M.; Thomas, R.E.; , "Carrier mobilities in silicon empirically related to doping and field," Proceedings of the IEEE , vol.55, no.12, pp. 2192- 2193, Dec. 1967

[5] Arora, N.D.; Hauser, J.R.; Roulston, D.J.; , "Electron and hole mobilities in silicon as a function of concentration and temperature," Electron Devices, IEEE Transactions on , vol.29, no.2, pp. 292- 295, Feb 1982

[6] Masetti, G.; Severi, M.; Solmi, S.; , "Modeling of carrier mobility against carrier concentration in arsenic-, phosphorus-, and boron-doped silicon," Electron Devices, IEEE Transactions on , vol.30, no.7, pp. 764-769, Jul 1983

[7] Klaassen, D.B.M.; , "A unified mobility model for device simulation," Electron Devices Meeting, 1990. IEDM '90. Technical Digest., International , vol., no., pp.357-360, 9-12 Dec 1990

[8] Shirahata, M.; Kusano, H.; Kotani, N.; Kusanoki, S.; Akasaka, Y.; , "A mobility model including the screening effect in MOS inversion layer," Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol.11, no.9, pp.1114-1119, Sep 1992

[9] Martino, J.A.; Pavanello, M.A.; Verdonck, P.B., Caracterização Elétrica de Tecnologia e Dispositivos MOS, Thomson, São Paulo, 2003.

[10] Conde, O. A.; Sánchez, F. J. G.; Liou, J. J.; Cerdeira, A.; Estrada, M.; Yue Y., A review of recent MOSFET threshold voltage extraction methods. Microelectronics Reliability, v. 42, p. 583-596, 2002.